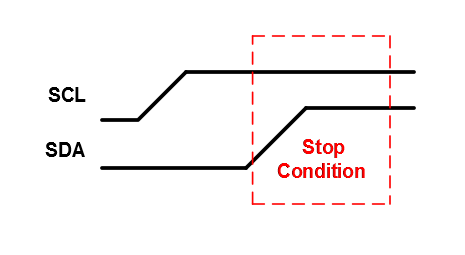

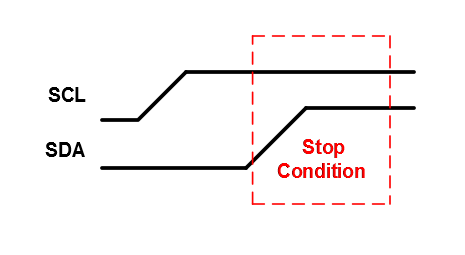

All I2C transmissions end with a Stop condition. A Stop condition occurs when the SDA line transitions from a logic low (active) level to a logic high (idle) level while the SCL line is at a logic high level. A Stop condition is always generated by the master device, and is generated by module hardware when a Not Acknowledge (NACK) is detected on the bus, a bus time-out event occurs, or when the I2C Byte Count (I2CxCNT) register reaches a zero count.

The figure below shows a Stop condition.

Figure 1. Stop Condition