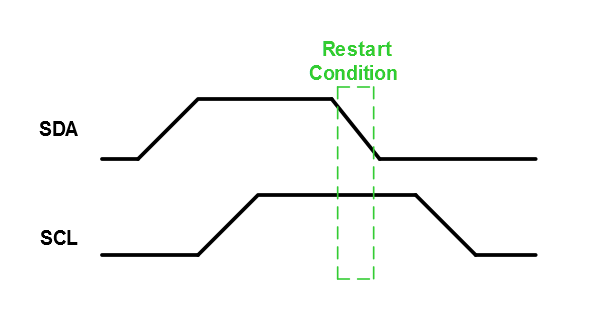

A Restart condition is essentially the same as a Start condition – the SDA line transitions from an idle level to an active level while the SCL line is idle – but may be used in place of a Stop condition whenever the master device has completed its current transfer but wishes to keep control of the bus. A Restart condition has the same effect as a Start condition, resetting all slave logic and preparing it to receive an address.

A Restart condition is also used when the master wishes to use a combined data transfer format. A combined data transfer format is used when a master wishes to communicate with a specific register address or memory location. In a combined format, the master issues a Start condition, followed by the slave’s address, followed by a data byte which represents the desired slave register or memory address. Once the slave address and data byte have been acknowledged by the slave, the master issues a Restart condition, followed by the slave address. If the master wishes to write data to the slave, the LSb of the slave address, the Read/not Write (R/W) bit, will be clear. If the master wishes to read data from the slave, the R/W bit will be set. Once the slave has acknowledged the second address byte, the master issues a Restart condition, followed by the upper byte of the slave address with the R/W bit set. Slave logic will then acknowledge the upper byte, and begin to transmit data to the master.

The figure below shows a Restart condition.