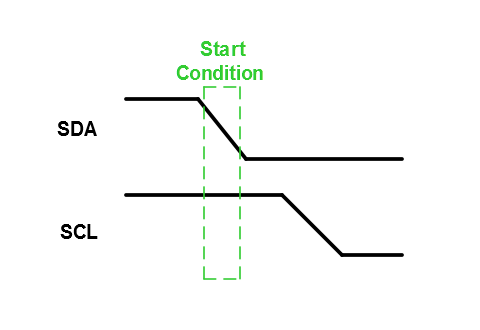

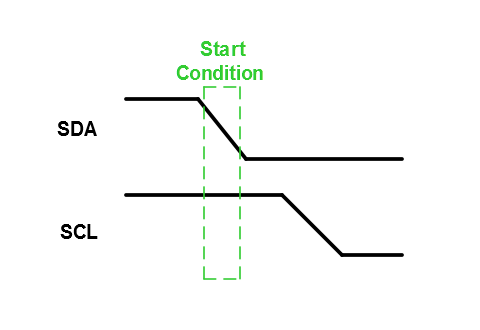

All I2C transmissions begin with a Start condition. The Start

condition is used to synchronize the SCL signals between the master and slave devices.

The I2C Specification defines a Start condition as a transition of the SDA

line from a logic high level (Idle state) to a logic low level (Active state) while the

SCL line is at a logic high (see figure below). A Start condition is always generated by

the master, and is initiated by either writing to the Start (S) bit or by writing to the I2C Transmit Buffer (I2CxTXB) register, depending on the Address Buffer Disable (ABD) bit setting.

When the I2C module is configured in Master mode, module hardware

waits until the bus is free (Idle state). Module hardware checks the Bus Free Status

(BFRE) bit to ensure the bus is idle before initiating a

Start condition. When the BFRE bit is set, the bus is considered idle, and indicates

that the SCL and SDA lines have been in a logic high state for the amount of

I2C clock cycles as selected by the Bus Free Time Selection (BFRET) bits. When a Start condition is detected on the bus, module hardware

clears the BFRE bit, indicating an active bus.

In Multi-Master mode, it is possible for two master devices to issue Start conditions at the same time. If two or more masters initiate a Start at the same time, a bus collision will occur; however, the I2C Specification states that a bus collision cannot occur on a Start. In this case, the competing master devices must go through bus arbitration during the addressing phase.

The figure below shows a Start condition.

Figure 1. Start Condition