The SMBus protocol requires a bus watchdog to prevent a stalled device from holding the bus indefinitely. The I2C Bus Time-Out (I2CxBTO) register provides several timer sources that can be configured as the time-out time base. When the selected resource expires, the module is reset and the bus is forced into an Idle state.

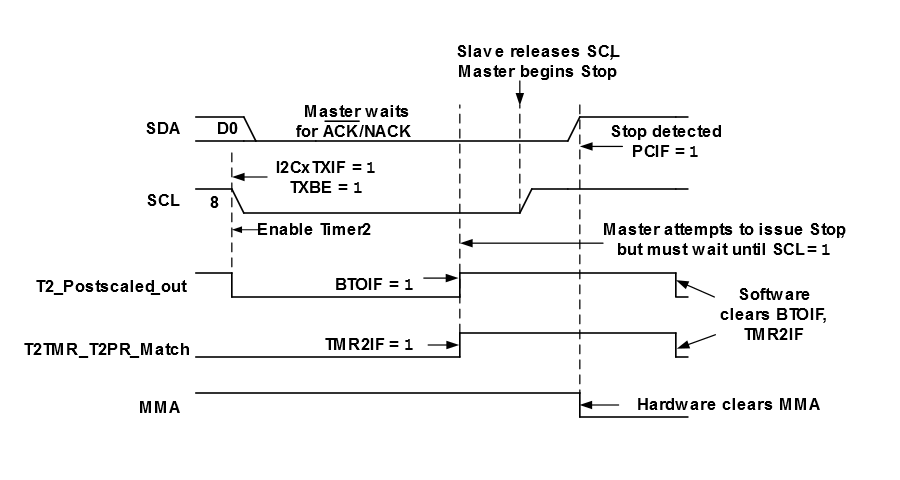

For example, Timer2 can be selected as the bus time-out source and set to begin counting when the SCL line is low. If Timer2 rolls over before the SCL line transitions high, the module is reset.

1), the module is immediately reset, the SMA

and Slave Clock Stretching (CSTR) bits are cleared, and the Bus Time-out Interrupt Flag (BTOIF) bit is set. If the module is configured in Master mode, and the bus time-out event

occurs while the master is active (Master Mode Active (MMA) = 1), the module will immediately attempt to

transmit a Stop condition, and sets the BTOIF bit. Stop condition generation may be

delayed if a slave device is stretching the clock, but will resume once the clock is

released, or if the slave holding the bus also times out. The MMA bit is only cleared

after the Stop condition has been generated.

The figure below shows an example of a bus time-out event when the module is operating in Master mode.